# New High Speed Switch Offers Sub-50ns Switching Times

**Application Note**

December 1993

AN543.1

#### Introduction

An ideal CMOS analog switch would exhibit such characteristics as zero resistance when turned on, infinite resistance when turned off, zero power consumption, and zero switching time. Unfortunately, such a device is usually found as an example in a college textbook. The real world offers trade-offs and imperfections which prevent the realization of the ideal. The integrated circuit designer works within these limits and attempts to optimize device performance by utilizing new technologies and improving circuit design. The development of a new high speed analog switch required the use of both of these techniques to achieve its performance. (See Appendix I: "Inside the HI-201HS").

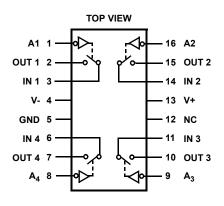

The Intersil HI-201HS is the industry's first sub-50ns monolithic analog switch and along with fast switching speed, offers improved performance and pin compatibility with industry standard 201's (Figure 1 ). This article will discuss the technology, performance, and applications for this product.

# Improve Those Existing Designs

The application circuits which follow are examples of typical applications and illustrate how the HI-201HS can improve existing applications where standard 201's are presently being used.

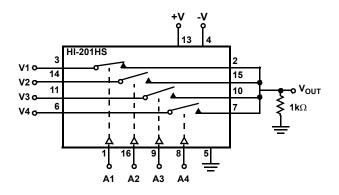

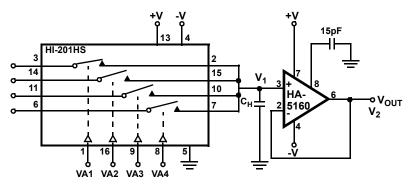

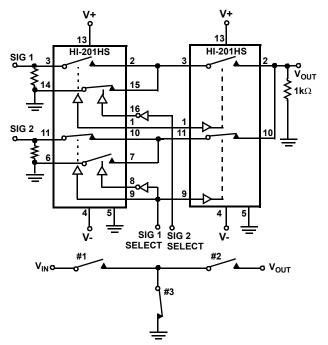

The first example is a high speed multiplexer shown in Figure 2. The analog multiplexer is a circuit which switches a number of analog inputs to a single output and is used heavily in data conversion and avionic applications. This function can be easily achieved with the HI-201HS by tieing the outputs together and selecting the appropriate analog input. The HI-201HS is an excellent choice for this application since its low on resistance and leakage current will reduce system error, and its high speed is unmatched by any other monolithic analog switch. Since the output capacitance is additive, the RC time constant of the load will increase when the outputs are made common.

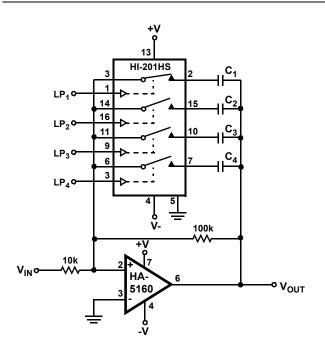

The next application is a high speed sample and hold which takes advantage of the improved performance of the HI-201HS and the precision F.E.T. input of the HA-5160 high slew rate amplifier. A sample and hold circuit, or track and hold as it is sometimes called, has two operating modes. In one mode the switch is closed and the capacitor charges to the input voltage. The second mode occurs when the switch is opened and the capacitor holds this charge for a specified period of time.

The speed of a sample and hold circuit is directly related to the switching device used and the output amplifier. This characteristic of a sample and hold circuit is called the acquisition time. It is defined as the time required following a "sample" command, for the output to reach its final value. The acquisition time includes the switch delay time, the time constant of the switch on resistance and hold capacitor (T =  $R_{ON} C_{HOLD}$ ), and the slew and settling times of the output amplifier.

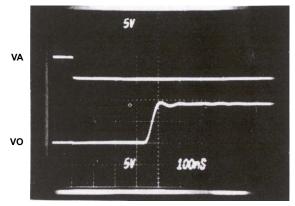

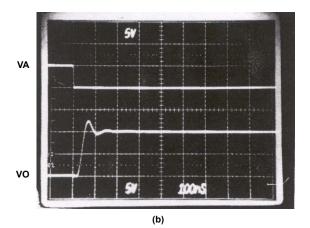

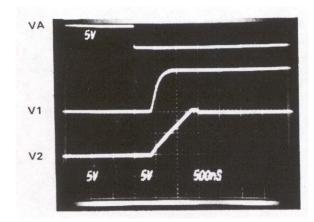

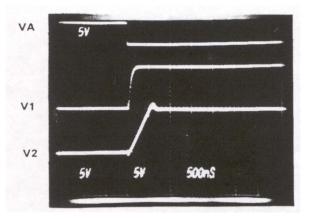

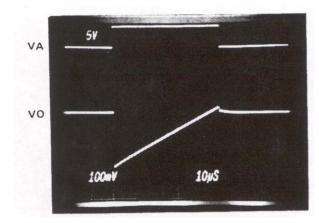

The photographs shown in Figure 3 illustrate the improvement in the acquisition time possible by using the HI-201HS. The first photograph represents the sample/hold circuit using a standard 201 switch and an HA-5100 operational amplifier. The first waveform is the "Sample" voltage ( $V_A$ ). The second waveform is the voltage on the hold capacitor ( $V_1$ ). And the third waveform is the output of the amplifier ( $V_2$ ).

The second photograph is the same circuit with a HI-201HS and on HA-5160 op amp. Comparison of the photographs shows the HI-201HS has significantly reduced the switch delay time and the high slew rate of the 5160 amplifier has also contributed to the reduced acquisition time.

A source of error in this circuit is a d.c. offset which is called sample to hold offset error. This error is primarily due to the charge injection (Q) of the switch and is related to the hold capacitance by the following expression:

offset error (V<sub>O</sub>) =

$$\frac{charge \ transfer \ (Q)}{C_{H}}$$

The reduced charge injection of the HI-201HS (typically 10pc) will result in immediate reduction of this error.

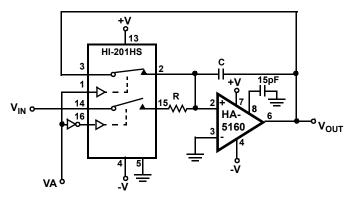

Using analog switches with operational amplifiers is common in circuit design. An example is shown in Figure 4 which is an integrator with start/reset capability.

| LOGIC               | SWITCH |  |

|---------------------|--------|--|

| $0-V_{AL} \le .8V$  | ON     |  |

| $1-V_{AH} \ge 2.4V$ | OFF    |  |

#### **TYPICAL SPECIFICATIONS**

| ANALOG SIGNAL RANGE | ±15V  |

|---------------------|-------|

| ON RESISTANCE       | 30Ω   |

| OFF LEAKAGE         | .3nA  |

| SWITCH ON TIME      | 30ns  |

| POWER DISSIPATION   | 120mW |

FIGURE 1. TYPICAL PINOUT AND SPECIFICATIONS - THE HI-201HS IS PIN COMPATIBLE WITH STANDARD 201'S AND OFFERS IMPROVED PERFORMANCE. SPECIFICATIONS GIVEN ARE TYPICAL VALUES AT  $T_A = 25^{\circ}$ C.

(a)

FIGURE 2. HIGH SPEED ANALOG MULTIPLEXER: (a) CIRCUIT RESPONSE USING THE STANDARD 201 ( $t_{access} = 400$ ns). (b) CIRCUIT RESPONSE USING HI-201HS ( $t_{access} = 50$ ns). THE ACCESS TIME IS DEFINED AS TOTAL TIME REQUIRED TO ACTIVATE AN "OFF" SWITCH TO THE "ON" STATE. ACCESS TIME IS NORMALLY MEASURED FROM THE INITIATION OF THE DIGITAL INPUT PULSE ( $V_A$ ) TO THE 90% POINT OF THE OUTPUT TRANSITION.

FIGURE 3A. HIGH SPEED SAMPLE AND HOLD: THE BASIC SAMPLE AND HOLD SAMPLES THE INPUT VOLTAGE WHEN THE SWITCH IS CLOSED AND THE CAPACITOR HOLDS THE VOLTAGE WHEN THE SWITCH IS OPEN. THE SPEED OF THE SWITCHING ELEMENT AFFECTS THE SPEED OF THE SAMPLE AND HOLD

FIGURE 3B. CIRCUIT RESPONSE TO A "SAMPLE" COMMAND USING A STANDARD 201 AND AN HA-5100 OPERATIONAL AMPLIFIER (AQUISITION TIME = 1.5µS)

FIGURE 3C. CIRCUIT RESPONSE USING AN HI-201HS AND HA-5160: HI-201HS SIGNIFICANTLY REDUCES SWITCH DELAY TIME (AQUISITION TIME = 500ns)

FIGURE 4A. INTEGRATOR WITH START/RESET: A LOW LOGIC INPUT PULSE DISCONNECTS THE INTEGRATOR FROM THE ANALOG INPUT AND DISCHARGES THE CAPACITOR. WHEN THE LOGIC INPUT CHANGES TO A HIGH STATE, INTEGRATOR IS ACTIVATED

FIGURE 4B. LOW LEVEL INTEGRATION - CIRCUIT RESPONSE USING STANDARD 201 SWITCH

The switch is used to apply the input signal and to reset the integrator. Applying a low logic level removes the input signal and the capacitor is discharged. When a logic level high is present, the input signal is integrated with a rate of change equal to:

$$dvo/dt = \frac{i_f}{c_f} = \frac{-V_i}{R_1 C_f}$$

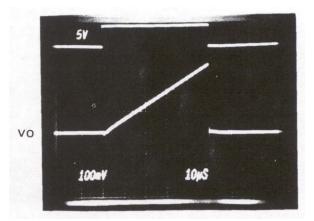

The reduced on resistance, leakage current, and charge injection of the HI-201HS will improve the performance of this circuit and an example of this improved peformance can be seen in the photographs in Figure 4. These photographs illustrate the reduced charge injection which the 201HS offers. The component values are  $R_1 = 1M\Omega$ , C = 150pF and  $V_{IN} = -1V$ . With these values, the amplifier will integrate the input signal with a slope of 6.6mV/µs. For a 50µs time period, the amplifier will integrate to a magnitude of  $\approx$  300mV. The photographs of the test results indicate this to be true, but it should be apparent that the two photographs are quite different. The first photograph represents the

FIGURE 4C. LOW LEVEL INTEGRATION - CIRCUIT RESPONSE ILLUSTRATES IMPROVED CHARGE INJECTION OF THE HI-201HS

amplifier output using a standard 201 as the reset switch. The second photograph is the same circuit with a 201HS.

The offset error in the first photograph is due to the charge injection of the switch. Using the expression  $Q = V \times C$  and knowing the standard 201 has a typical charge transfer of 30pc, this offset can be calculated.

V = Q/C = 30pc/150pf = 200mV

Other examples of combining switches and amplifiers are shown in Figures 5 and 6. In both these applications the switch is used to tailor the amplifiers performance. Figure 5 is a low pass filter with a selectable break frequency.

FIGURE 5. LOW PASS FILTER WITH SELECTABLE BREAK FREQUENCY - SWITCH SELECTION PLACES VARIOUS VALUES OF CAPACITANCE IN PARALELL WITH THE FEEDBACK RESISTOR. THE VALUE OF THE CAPACITOR DETERMINES THE BREAK FREQUENCY. THE BREAK FREQUENCY IS THAT FREQUENCY AT WHICH THE SIGNAL BEGINS ATTENUATION

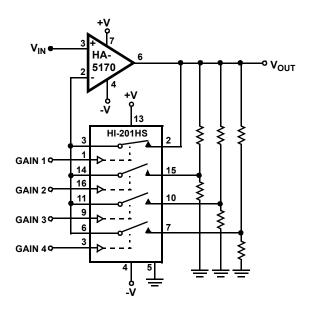

#### FIGURE 6. AMPLIFIER WITH PROGRAMMABLE GAIN -SWITCH SELECTION ACTIVATES A NEW VOLTAGE GAIN WHICH IS DETERMINED BY THE RESISTIVE FEEDBACK

Depending on which switch is selected, a particular cutoff frequency is introduced by the expression:

$$F_{\rm C} = \frac{1}{2\pi R C_{\rm x}}$$

A programmable gain amplifier is shown in Figure 6. Similar in function to the filter application, the gain of the amplifier is determined by selection of a switch.

When using switches with other components it is important that a switch be selected which introduces a minimal amount of error to the circuit. Operational amplifier gain error due to high on resistance or offset voltages due to excessive leakage current and charge injection are examples of potential errors created by the switch. The previous applications have demonstrated that the 201HS offers improved performance by minimizing circuit error and increasing system speed.

# On The Drawing Board

Since the introduction of the HI-201HS switch, many engineers have expressed an interest in using this new product. Although much of their work is in a preliminary stage and they do not want to divulge exact details on their designs, the following information is intended to give you an idea of how other engineers are considering using the HI-201HS.

The majority of the engineers are interested in taking advantage of the products fast switching speed. One particular engineering group is investigating replacement of DMOS (double-diffused MOS) transistors with the HI-201HS.

The DMOS transistor is capable of extremely fast switching speeds (1ns) and until now, switches fabricated using CMOS technology have not been fast enough to be considered. But the HI-201HS is attractive since it offers unprecedented switching speed along with the established benefits of CMOS technology. Such benefits include a wider analog signal range capability and lower operating power requirements.

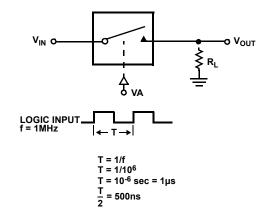

A common application for analog switches is time division multiplexing, where many signals are processed on a single channel. High speed switching allows higher information capacity on the channel, since the switching speeds of an analog switch are directly related to the maximum switch activation frequency. The faster a switch can turn on and off, the higher the possible switching frequency. An example of this relationship is shown in Figure 7. If a switch is activated at a frequency of 1MHz, it must turn on and off within a 500ns time period. Since the HI-201HS has a maximum on and off times of 50ns, and can turn on and of within a 100ns time period, it theoretically possible that it can be activated at a 5MHz frequency rate. This improved capability is making the HI-201HS an attractive component to design engineers requiring high frequency data processing. Conversations with engineers indicates that possible applications are computer graphics and visual display circuit designs.

#### FIGURE 7. HIGH FREQUENCY SWITCHING - HI-201HS FAST SWITCHING TIMES ALLOW IT TO TRANSFER DATA AT A HIGHER RATE OF FREQUENCY.

Another area where the HI-201HS is generating interest is in the area of medical electronics. This is a growing field and improvements are continously being made as products become available. Much of the medical equipment being designed requires both high speed and accuracy.

Medical test equipment is primarily used to transmit or receive information from the patient. An example where both of these functions are used is in the area of ultrasound. Ultrasound testing requires that a signal be transmitted to the patient and the return signal is then amplified and displayed or recorded. The 201HS is being considered for the use in such an application and would be used to control the transmission and reception of these signals.

FIGURE 8. VIDEO SWITCHING WITH IMPROVED ISOLATION -IMPROVED HIGH FREQUENCY OFF STATE PERFORMANCE IS OBTAINED BY USING A T-SWITCH CONFIGURATION. WHEN TWO SERIES SWITCHES ARE OFF, THE THIRD SWITCH IS SHORTED TO GROUND

The designers are not only interested in fast switching speed, but also in low on resistance. This is an important aspect of the switch since many of the electrical signals in medical electronics are of a small magnitude. An example is patient monitoring equipment which converts physiological parameters into electrical signals. If these low level electrical signals require switching before amplification, a low on resistance switch is essential to minimize the voltage drop across the switch itself. The low on resistance of the HI-201HS enables it to be used in applications using signals of smaller magnitude. Video circuit design involves the control of high frequency signals. Applications which require the switching of these high frequency signals are usually limited by the off isolation and crosstalk performance of the switch. Off isolatron is defined as the amount of feedthrough of an applied signal through an off switch. Crosstalk is the amount of cross coupling of an "off" channel to the output of an "on" channel. Both of these switch characteristics will degrade as the frequency of the input signal increases.

The HI-201HS has some improvement over the standard 201 in these areas but the configuration shown in Figure 8 is being used by designers to improve the isolation capabilities of CMOS analog switches. This configuration is known as "T" switching since the three switches used for passing the signal could be thought of in the shape of the letter T. The simplified figure shows that when switches #1 and #2 are off, switch #3 is tied to ground. When switches #1 and #2 are on, #3 is off. This improves isolation by having two channels in series off and any feedthrough is fed to ground.

# Conclusion

The Intersil HI-201HS is the fastest monolithic CMOS analog switch available. It offers improved performance for existing designs and should be considered for use in any application where switching speed is an important criteria.

# Acknowledgements

The author would like to thank Gary Maulding, Frank Cooper, and Bob Junkins for their technical assistance, Ken Timko and Dick Whitehead for their editorial comments, and the dynamic duo of Lilly Andrews and Kathy Glines for their secretarial skills and patience in the preparation of this paper.

#### References

- 1. D. F. Stout, "Handbook of Operational Amplifier Circuit Design". New York: McGraw-Hill, 1976.

- J. G. Graeme, G.E. Tobey, and L. P. Huelsman, "Operational Amplifiers: Design and Applications". New York : McGraw Hill, 1971.

- 3. J. A. Connelly, "Analog Integrated Circuits" New York: John Wiley & Sons, 1975.

- 4. HA-2420/2425 Fast Sample and Hold data sheet, Harris Semiconductor .

# Appendix I-Inside the HI-201HS

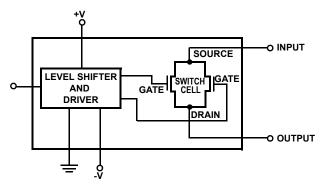

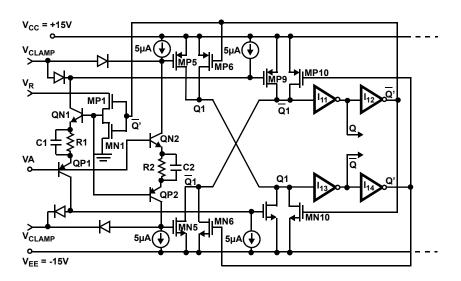

The HI-201 is a TTL compatible quad CMOS analog switch which features switching times under 50ns and a typical "on" resistance of  $35\Omega$ . The fast switching times are achieved through a combination of process and circuit design techniques. The HI-201HS is fabricated using a dielectric isolation process with complementary PNP and NPN bipolar transistors and polysilicon-gate CMOS. The use of bi-technology process enabled a unique circuit called a D.C. Static Level Shifter to be designed.

The typical CMOS analog switch consists of a switch cell which is driven by a level shifter. The level shifter converts a single logic input into two complementary outputs which drive the gates of the CMOS switch cell (Figure A). The switch cell represents a capacitive load to the level shifter, so fast switching times require large drive currents to charge these capacitances quickly. The D.C. Static level shifter circuit (Figure B) provides large drive currents only when switching and dissipates little power in a quiescent condition.

The D.C. static level shifter achieves high switching speeds through the use of a unique bipolar input stage and a network of switching and holding MOS transistors. Devices MN5, MP5, MN9 MP9 are the switching transistors and MN6, MP6, MN10, MP10 are the holding transistors. The major advantage of the bipolar input transistors is that its transconductance (gm) is much higher than that possible with F.E.T. transistors. To understand the level shifter operation, consider a change of logic input from low state to high. Initially VA is low, Q = Q1 = Q' = -15V and  $Q = Q_1 = Q' = 15V$ . VB is at ground and QN2, QP2 are off. When VA goes high, QP2, QN2 turn on, which slew the gates of switching devices MN5, MP5 with a current 1 =  $(VA - 2V_{BF})/R$ . The switching devices overcome the holding devices, MN10, MP10 and switch the internal nodes Q1, and Q1. CMOS buffers I11, I13 provide large drive currents to the switch cell, while inverters I12, I14 provide delayed feedback signals. The feedback signals turn off holding devices MN10, MP10 while turning on holding devices MN6, MP6. The feedback also turns on QN2, QP2 by means of MN 1, MP1. These feedback signals have returned the level shifter to a static condition by turning the bipolar input stage and MOS switching transistors off .

FIGURE A. SIMPLIFIED I.C. ANALOG SWITCH OPERATION -LEVEL SHIFTER CONVERTS LOGIC INPUT INTO DRIVE SIGNAL FOR CMOS SWITCH CELL

FIGURE B. SIMPLIFIED D.C. STATIC LEVEL SHIFTER - THE LEVEL SHIFTER CONSISTS OF A UNIQUE BIPOLAR INPUT STAGE AND A NETWORK OF SWITCHING AND HOLDING DEVICES

Similar operation occurs when VA goes from high to low. bipolar transistors QN1, QP1 turn on MN9, MP9. The feedback resets the holding devices and turns off the bipolar input stage.

# Appendix II-HI-201HS vs. Standard 201

The use of a dual technology process and a creative design improves the performance of this analog switch. The following table illustrates the results of this combination by comparing the specification of the HI-201HS with the standard 201.

It should be apparent from Table 1 the substantial improvement in switching speeds offered by the HI-201HS. But since the switch "off" time of the high speed switch is measured differently from the standard 201, a brief discussion of test methods will avoid any confusion.

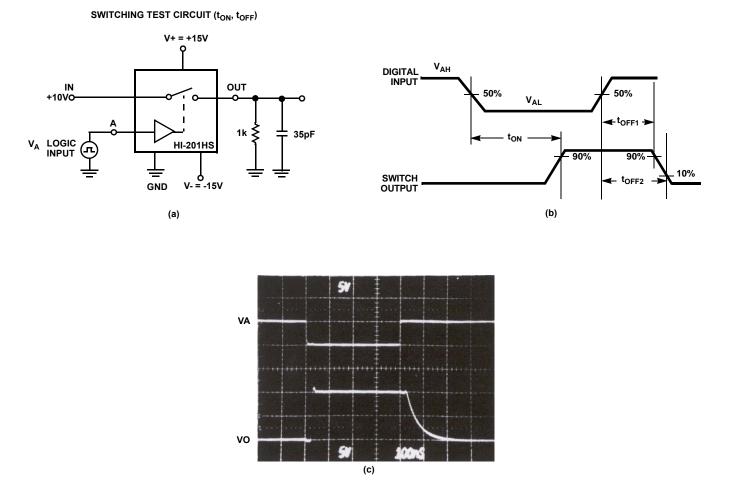

Figure A is a typical switching time test circuit for an analog switch. The "on" time is measured from the logic input to the 90% point of the output.

The "off" time can be measured from the logic input to either the 90% or 10% point of the output. This variation in the "off" time test point is due to the dependence of the measurement on the load. The dominant component of the switch "off" time is an exponential RC time constant determined by the values of the load resistance and capacitance. The "off" time of the HI-201HS is measured to the 90% point. The RC time constant due to load is excluded from this measurement. The photograph included in Figure A is a typical HI-201HS switching time response.

The remainder of table 1 compares other critical specifications of CMOS analog switches. The HI-201HS is not only a high speed switch but also offers improved performance in other areas. The parameters of "on" resistance, leakage current, and charge injection can all

8

contribute unwanted errors to system level applications. With the improvements shown in these areas, the HI-201HS offers potential improvement in system accuracy for a wide variety of applications and since the HI-201HS is pin compatible with existing 201s, the high speed version can be plugged into existing designs for immediate improvement in performance.

The HI-201HS is an improvement over the standard 201 in many areas, but some trade-offs still exist. One such tradeoff was the power dissipation of the product. In order to meet the high speed criteria, larger internal currents are needed which in turn demand increased supply current. But this apparent shortcoming is more than offset by the products performance.

| ,                                                         |                    |                      |                    |  |

|-----------------------------------------------------------|--------------------|----------------------|--------------------|--|

| PARAMETER                                                 | TEMPERATURE<br>(°) | INTERSIL<br>HI-201HS | INTERSIL<br>HI-201 |  |

| Switching Speed<br>t <sub>ON</sub><br>t <sub>OFF</sub>    | 25<br>25           | 50ns<br>50ns         | 500ns<br>500ns     |  |

| ON Resistance                                             | 125                | 75Ω                  | 125Ω               |  |

| Leakage Current<br>I <sub>SOFF</sub><br>I <sub>DOFF</sub> | 125<br>125         | 100nA<br>100nA       | 500nA<br>500nA     |  |

| Charge Injection<br>(Q)                                   | 25                 | 10pc (typ)           | 30pc (typ)         |  |

| Power Dissapation<br>(Pd)                                 | 125                | 240mW                | 60mW               |  |

#### TABLE 1. SPECIFICATION COMPARISON: IMPROVED PERFORMANCE OF HI-201HS OVER STANDARD 201s (ALL VALUES ARE MAXIMUMS UNLESS STATED OTHERWISE)

FIGURE A. SWITCHING TIME TEST CIRCUIT: (a) SWITCHING TEST CIRCUIT, (b) SWITCHING WAVEFORMS, (c) TYPICAL HI-201HS RESPONSE

Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that the Application Note or Technical Brief is current before proceeding.

For information regarding Intersil Corporation and its products, see www.intersil.com